Intel® Stratix® 10 裝置完成配置並進入使用者模式後,您必須執行重設序列才能執行應用程式。在完成設定階段後,Intel Stratix 10 裝置的功能預計不會同時進入使用者模式。當裝置進入使用者模式時,自由運行的頻率可能會在使用者邏輯之間造成時鐘賽跑狀態,進而破壞裝置初始條件。

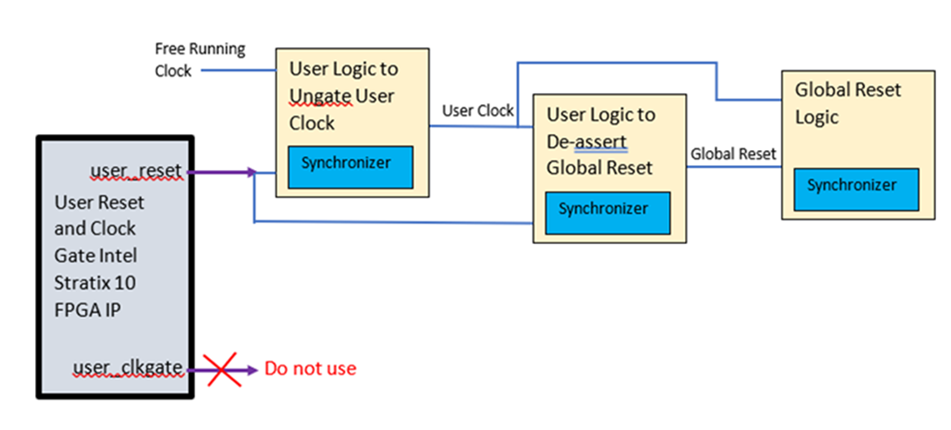

為了防止發生此事件,Intel 建議您使用使用者重設和頻率門Intel Stratix 10 FPGA IP,並採用您自己的使用者邏輯來建立設計,以取消使用者頻率的閘道,並取消維護圖 1 所示的全球重設訊號。使用使用者重設和頻率閘門 Intel Stratix 10 FPGA IP 核心來除去從user_reset埠發出的訊號以解關使用者頻率。然後建立自己的邏輯,在您取消使用者頻率閘道後,解認「全域重設」訊號。

請注意, 免費運行頻率是外部來源的頻率,同時使用者 頻率是一個在FPGA中為使用者邏輯計時的頻率。 使用者頻率 也可以是一個免費的運行頻率或一個相鎖迴圈 (PLL) 產生的頻率。

預計只需要一個 IP 實例即可卸載所有使用者頻率,同時應使用全球重設訊號在多個領域中釋放/解認重設。如果設計具有多個重設領域,請確保全球重設訊號保持足夠長的時間,使訊號在移除之前傳送到所有領域。

圖 1。使用者重設和頻率 Gating Block 圖表

注意:請勿使用使用者重設和頻率門 user_clkgate 埠Intel Stratix 10 FPGA IP。

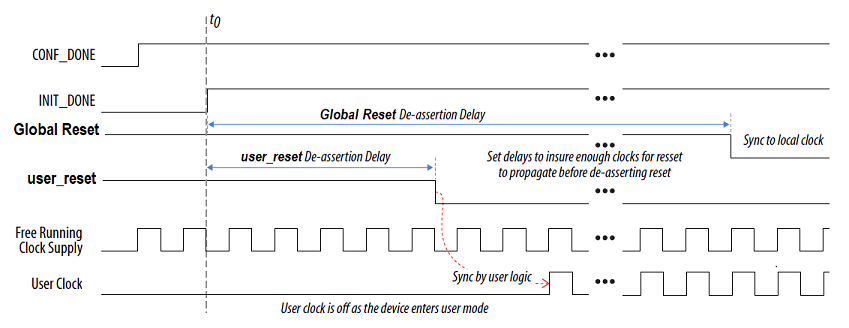

使用Intel Stratix 10 FPGA使用者重設和頻率門 IP,以及全球重設訊號的除錯延遲,建議user_reset訊號的除錯延遲

user_reset訊號除錯延遲必須超過一個使用者頻率週期。您可以在 10 FPGA IP 中,在使用者重設與頻率閘門中輸入去塞塞延遲值Intel Stratix,獲得所需的延遲。10 FPGA IP 在使用者重設與頻率 Intel Stratix門中除錯延遲參數的可能值範圍從 0 ns 到 65,535 ns。您必須在內部使用標準的抗轉移技術建立同步器:

- 解封使用者頻率的使用者邏輯,將user_reset訊號與免費運行頻率同步。

- De-assert Global Reset 的使用者邏輯,將user_reset訊號與使用者頻率同步。

全球重設訊號除錯延遲必須足夠長的時間,才能讓Global Reset訊號在User Clock 執行後,在您的系統中傳播到全球重設邏輯。建立您自己的使用者邏輯,在除user_reset並執行User Clock 後,解說「全球重設」訊號。您還必須使用標準的抗轉移技術,針對使用者頻率同步「全球重設」訊號。

圖 2。使用者重設和頻率 Gating 計時圖表

此資訊記錄在 Intel® Quartus® Prime Pro Edition 軟體 v19.1 的最新Intel Stratix 10 組態使用者指南 中。