由於缺乏適當的 JTAG 限制,在 Intel 收發器工具組載入具有多塊磚上通道的設計時,您可能會看到 Intel® 收發器工具組中「無法抓住通道 TX/RX/LINK|* 設定」的錯誤。由於原生實體層軟邏輯的放置,當您在不同磚上有多個原生實體層即時時,最常觀察到問題。

解決方案是限制將重新設定的頻率喂到 Native PHY 的重新配置埠。確認「altera_reserved_tck」和連接到 Native PHY 的重新配置頻率埠的頻率「rcfg_clk」均已適當受限,並在 TimeQuest 內通過計時。此頻率用於Altera除錯 Mater Endpoint (ADME) 邏輯,收發器工具組會使用這個邏輯來存取收發器的 CSR 空間。只要您在設計中至少有一個經由 SDC 命令「create_clock」宣告的頻率,它就會代表您自動受限。若要驗證 JTAG 已自動受限,請透過輸出此訊息的quartus_fit:

「在 JTAG 訊號中加入預設計時限制。 這有助於實現基本功能,因為使用者沒有提供這樣的限制。」

或者,您可能希望更準確且手動限制 JTAG 頻率。 為此,Quartus 提供了 SDC 計時範本。

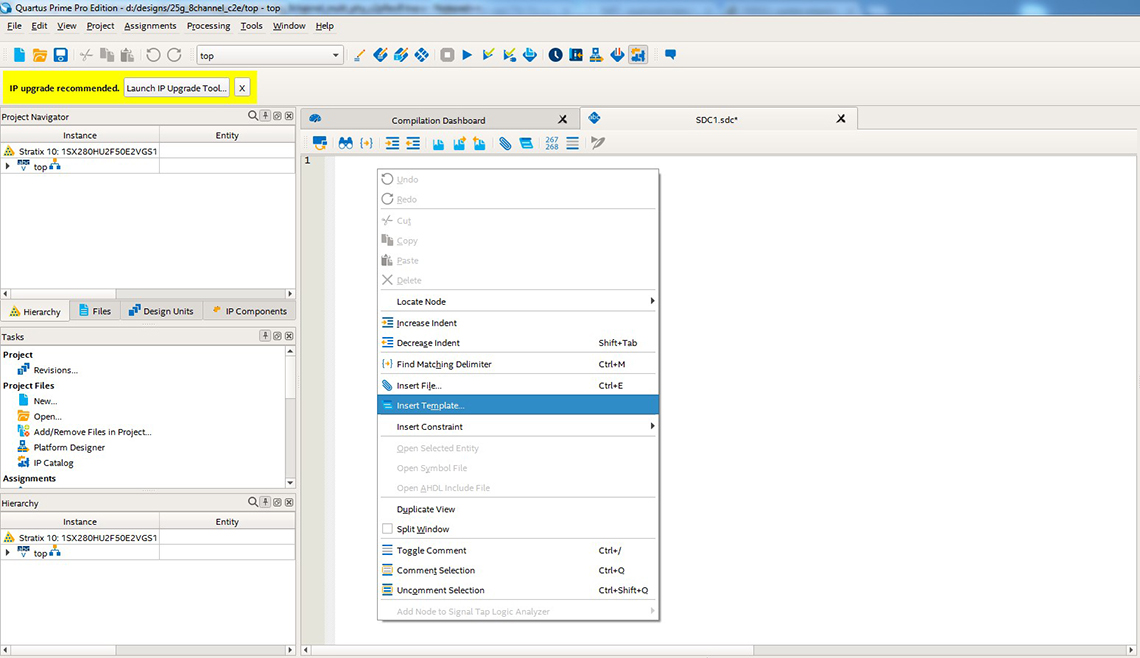

(1)具有 Quartus Prime 專業版的開放式 SDC 檔案 (檔案 ->開放)

(2)在 SDC 檔案視窗中按一下滑鼠右鍵以彈出功能表

(3)選擇「插入 Templete」

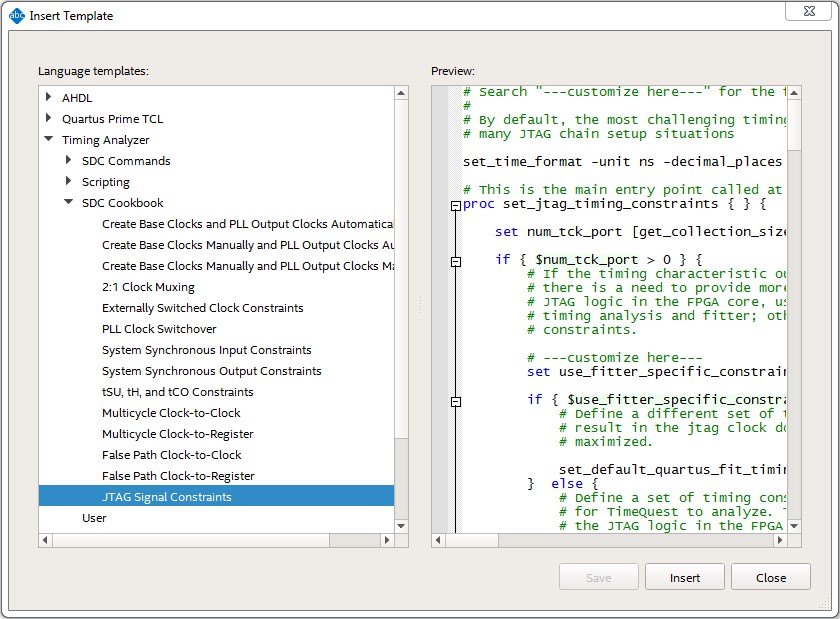

(4)選取「JTAG 訊號限制」,將限制插入 SDC 檔案。